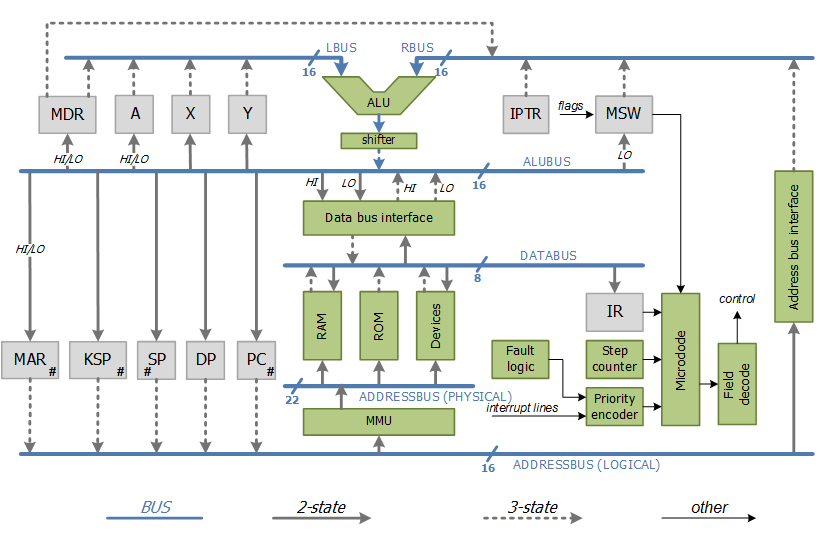

The following is a high level description of the computer’s current features and capabilities.

CPU architecture and technical details

- Modified Harvard Architecture

- 16-bit processor (combined 16/8-bit datapath)

- 16-bit logical address bus with separate code and data segments (128kb memory addressable by programs)

- 22-bit physical address bus (4MB total memory, 1MB currently installed)

- Programmable MMU

- 6 programmer visible registers

- Supervisor and user modes

- 256 opcodes (proprietary instruction set, similar to x86), see downloads for latest instruction set specs

- 7 distinct addressing modes (register, implied, immediate, register indirect, register indirect with offset, PC-relative, stack relative)

- 16 priority driven independent faults and interrupts

- Maximum tested CPU clock frequency is 4.09MHz

- Power draw is 11.5 watts (2.3A at 5V)

Peripherals

- 2 serial ports (RS-232)

- Real-time clock

- IDE controller

Current block diagram of the CPU